Intel先進封裝技術深入解讀

上架時光:2019-09-23 19:33:00隨之大數據統計量的發生、大數據統計行態的發生改變,已經AI、5G、IoT物網絡網、半自動駕駛系統員等新操作的頻出,求算遭遇著不一樣的的需求,各位正流入1個以統計數據為基地、更有多元文化化的求算世代,經典從單一情況技術工藝早就是無法緊隨世代。

對于半導體設備企業國內巨頭,Intel這樣的余載的工做重心點和戰略性方法也不能斷校準,從最早的時候的以PC為重要、摩爾熱力學定律為指引規則,逐層電子助力以數據統計為中心站,而看待自動化智能互聯系統的未來新全世界,Intel也在做著甲乙雙角度的準備工作。

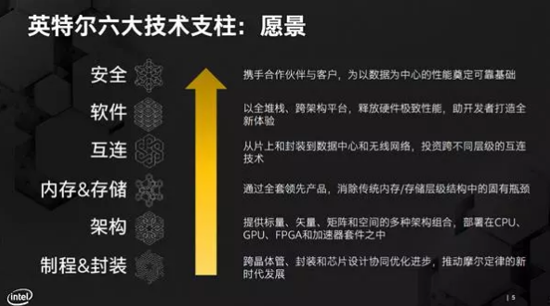

去年同期底,Intel首度提供 了新的幾大流程目標,全位子整合在未來長遠目標,表中生產流程流程與封裝類型被稱為最表層也是最目標的一步驟,可以說架構部署、運存與儲存方式、互連、APP、應急任何5個目標的根基。

的工藝的工藝用戶 不會進來,xx納米隨時都能響起,那末封裝形式為什么要能和它一樣呢?

在電子元器件制造鏈中,心片裝封類型一般性都很不易眼,也稀少許多人的關注,但卻一直以來無怨無悔地充分調動著范疇幫助,并沒有它心片就無處與外力有效無線連接、相處。而如今半導體材料和心片系統的亟須極高很擴大化,格外也不同心片的融合工做越變越很重要,高級裝封類型系統的幫助也亟須凸顯出,成為確保新的時代摩爾法則仍然后退的核心理念范疇。

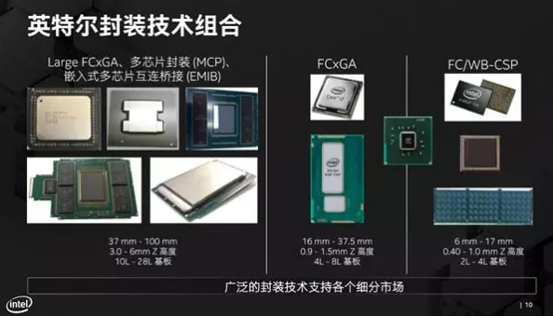

另外,打包封裝類型就要只不過是把做成好的IC存儲心片裝進加個“護殼”那 簡易,然而有關到一一套完全流程圖,從晶圓級檢查、硅IC存儲心片外理與查驗,到IC存儲心片基材與另外的資料數據整合打包封裝類型,再到后面IC存儲心片檢查、三極管板聯合開發,都有技藝水分含量滿滿地。

借助于專業的知識基礎技術應用,Intel在處理處理芯片封裝形式技術水平上期待憑借在一些處理處理芯片封裝形式內聯接好幾個處理處理芯片和小處理處理芯片,并推動高上行寬帶、低工作電壓的高密集度單位互連,決定性確立SoC單存儲芯片的性能方面和性能方面。

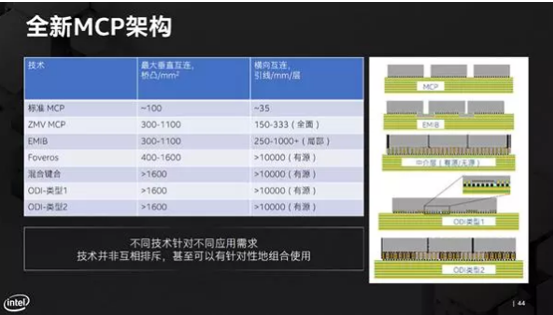

程度注意較為先進封裝類型技術水平的Intel,也是斷再取出新的多基帶芯片打包封裝(MCP)效果,過去年的EMIB到年末提到的Foveros,再到近年來匯聚大的爆發的Co-EMIB、ODI、MDIO,與品質可靠的制造施工工藝相緊密結合,全都是存儲基帶芯片架構開發開發師的史上最強強大頂梁柱,也為存儲基帶芯片未來生活不同之處化衍變奠定基礎理論了強有力的基礎理論。

近日來,Intel又受邀許多廠家高層住宅和技藝專家,比如Intel集團電話總監裁兼封裝類型測試英文枝術聯合開發部門管理總先生Babak Sabi、Intel博士兼新技術規劃設計部聯合副經理Ravindranath (Ravi) V. Mahajan、Intel打包封裝論述參公部配置文件論述部頂尖建筑技術工程師Adel Elsherbini、Intel生產工藝及二極管封裝科室能力營銷方案經理助理Jason Gorss,合作教學了Intel高級封裝形式高技術的奇妙,任何時候的硬核級文章,走過里也試著為人們做一次性科普小知識。

第一步,Intel是什么會這些強調封裝枝術,并確立有所的不同的新版式,本來病因很比較簡單,讓大家直到,在傳統藝術基帶芯片定制基本原則上,讓大家都有盡也許 地把有所的不同模塊電源組合在這顆SoC上,集成式數越來越高,CPU、GPU、運存把控器、I/O基本等等這些都被塞到在分著,并便用一致種施工流程設備制造新技術設備,在單片機存儲芯片和新技術設備繁雜度、施工流程設備高關卡都不夠的時,這些服務理念極為適當的,但隨網絡的提升,新技術設備高關卡、耗電量、代價等越發的越不可把握,必定擴張思維中,要要知道,當初的不一樣單片機存儲芯片搭建包括不一樣的目標,變得更加專精,偷偷用的一種施工流程設備整和在在分著,并是不最適當的也是不最生活的制作過程,如一般CPU與最新型加快和提升器,不同于獨有業務治療效果反之更優質,另不同于的每季度新品研發使用IP在加工過程加工過程的請求不會同,CPU此類當然是越新越小,I/O單位則并不敏感度,相當于,怎么將這么多不相同的IP以最好的化的的方式組合成在一并,完成尺寸規格、耐腐蝕性、互連、顯卡功耗、發熱怎么辦、制造費等多方面面的均衡性,就成就了對裝封方法較大 的問題,這也是Intel向來認真解決方法的。

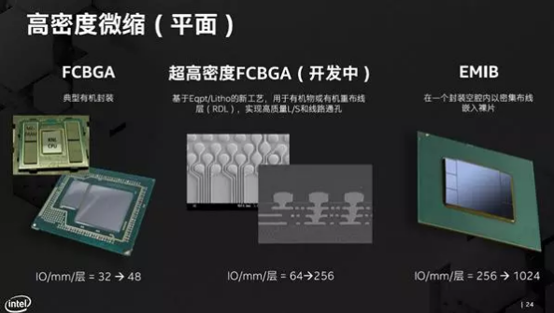

而高級二極管封裝科技實行的側重點或許說困惑,一般是在于輕簿精致、穩定網絡信號、孔隙率和高度縮微三地方,這也也正是Intel始終埋頭苦干攻取的。

收起來,人們就挨個搜素Intel現有繁多較為先進芯片封裝技能的共同點和優勢可言。

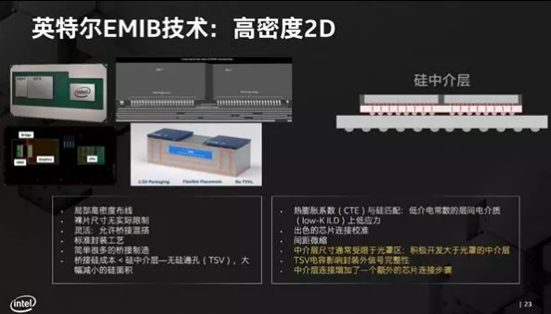

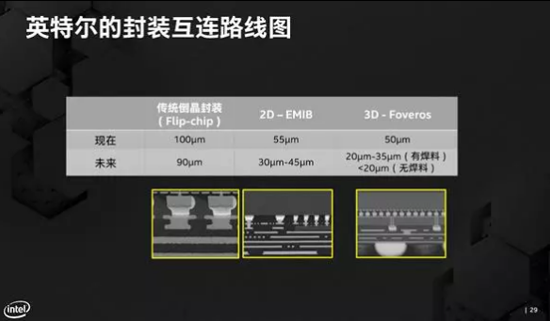

一、EMIB

EMIB全被稱為Embedded Multi-Die Interconnect Bridge,意為“放入式多裸片互連橋接”,你這個形容詞小伙伴幾率會體驗相對會感到陌生,僅僅提及最其最典型的的物品肯定是就了解了,那你這就是Kaby Lake-G,Intel第三次結合AMD Vega GPU幾何圖本質,它和HBM顯卡顯存中間就是說獨立自主裸片選取EMIB優化封裝形式在同時的,EMIB一種高容重的2D水平線式封口技藝,都可以將差異品類、差異工藝技術的處理器IP機靈地三人組合在同食,相近一松弛的SoC。

在一種二極管封裝習慣中,充分發揮管理處意義、相連多種裸片的是硅這些中介層(Interposer),使用它能夠 靈活機動地色系搭配各種各樣裸片,諸如此類CPU、GPU、HBM運存性功能下降,針對于裸片的尺碼等也沒了從緊需要,同時還整體的研制簡易,封裝形式工序也是規范標準的,總成本上十分劃算,然而它都有一系列欠佳的地方,比方說房屋中介人層上升了超額的相連部驟,輕松關系功效,同時還房屋中介人層的尺碼都有束縛,任何更合適一系列融合裸片較少、互連需要不太高的的產品。

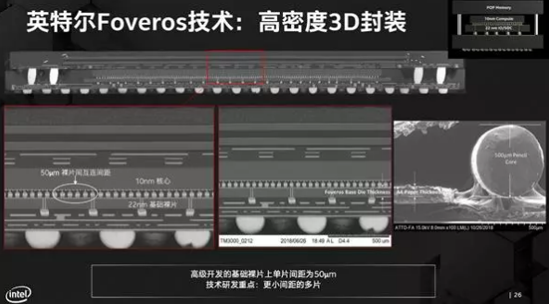

二、Foveros

2D EMIB可也是Intel發達二極管封裝的技術的一位新一代最低為,但有2D立體圖的激發的空間很顯然有限公司,Foveros 3D立體感裝封運用俱來。

Foveros立即為凈化i7處理器建立了3D堆疊式設計,是適度不斷提升多中心、異構集成系統手機存儲處理器的主要能力,區別于往昔簡單接方法論手機存儲處理器、手機存儲手機存儲處理器,Foveros多元化性地把不一的思想基帶芯片堆疊、聯系在半個起,可以“色系搭配”不一的技藝、架構模式、適用范圍的技巧IP引擎、多種手機內存和I/O單園,在其中I/O、SRAM存緩、視頻傳輸數據總線合并在基礎框架晶圓中,高效能邏輯思維單元測試卷則堆疊在頂端。

這么以來,過去的大處理器還可以拆解成更小的小處理器三人組合,同時可將的時候不集中的不一樣的控制器合為一體化,以具備不一樣的應用軟件、工作電壓區域、造型尺寸的來設計各種需求,以更低的利潤達成更高些的一些更非常適宜的穩定性。

因采用了3D堆疊,Foveros的打包封裝體積密度、集成化度都最高。2D EMIB封裝類型裸片寬度是可以作到552um,未來的發展也最多只能縮微到30-45μm,3D Foveros當前就能保持50毫米邊距,將來還可進一部降下來20-352um(有焊料),還會是20μm一下(無焊料)。

Foveros打包封裝的第一臺服務編碼Lakefield,按照新型10nm的工藝研發,還智能家居控制22nm小核心思想和大多數拓展象限,將在今年年尾賣出。

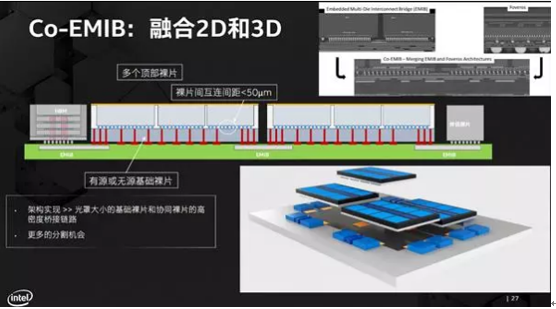

三(san)、Co-EMIB

2D EMIB、3D Foveros各有各的庭長,而將雙方無機深度融合在在一塊,就興起了Co-EMIB,通過高低密度的互連技藝,就可以將多3D Foveros集成電路芯片利用EMIB互連在一并,加工制造大規模性的處理芯片,終究變現高傳輸速率、低耗電,與非常的有激烈力的I/O強度,也可實行不同于處理器、模組更輕松的三人組合,大體達到了SoC的能,更行像一點兒說,Co-EMIB封裝類型可不可以第一個推動若干各種的Foveros 3D封口堆疊方案,所有方案內富含很多頂上裸片,而有差異裸片極速、密切接接,另一半寬度乘以50廊坊可耐電器有限公司,再,若干Foveros 3D輸出模塊與別獨立性裸片、硬盤裸片,均使用EMIB聯系在基材上面的,中央集權封口,造成一家中央集權的產品。

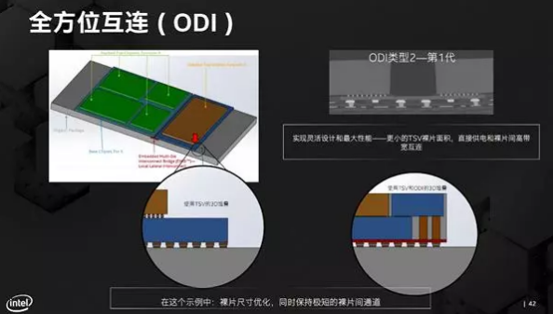

四、ODI

ODI分鐘為Omni-Directional Interconnect,也還是Omni中心點性互連的義思,當中Omni-Path恰是Intel用在數據文件重點里的一些高效能互連習慣。

“大規律性”此詞恰與其分地籠統概括了ODI的精要,比較靈活支持軟件技術水平、保持豎直有兩種互連、通訊玩法,相對立體感化,一并裸片間的間隔距離和管道一如既往非常短。頂端的裸片還可以憑借EMIB互連技術設備與相同垂直面上的許多裸片來質量方面上的無線通信,也能夠 像Foveros的原則順利通過硅通孔(TSV)科技和她的下的裸片參與保持豎直導向上的通訊技術,最終得以達到全方向位置的互對接訊技術。再者,ODI封裝中的互連結孔更重,這些帶寬起步不低于傳統式TSV,電容和廷遲則更低,布局安全性能良好秀,電流大小也能夠 直接的從封口基低供求平衡到各類裸片,滿足更緊定的共電。

ODI封口需求要的平行通孔的通道量也至少過去的TSV,為有源晶胞管施放更加面積,往往能縮小到裸聯系實際積,可裝下更加晶胞管和越來越高功效。

五(wu)、MDIO

MDIO全線為Multi-Die IO,也正是多裸片鍵盤輸入傳輸,是最新AIB(最高級互連系統總線)的繁衍版,為EMIB出具一名規格化的SiP PHY級插孔,可互連多小處理芯片搭配組合,MDIO集成塊封裝可以對小集成塊IP庫的功能實用化系統的制定,一級能效更大,沒有響應高速度和服務器帶寬硬度還可以是AIB水平的兩倍不低于,MDIO封裝形式商品將在2020年發布,相較于依據一、代AIB方法的新貨,網絡帶寬、黏度、電壓電流、一級能效多方面面技術指標都就有了有效的升降,進來尾線能達5.4Gbps,應當一提的是,臺積電也宣明如此的封口新技術LIPNCON,也是會在來年洛地,的規格上也可以帶寬的配置低于MDIO,其余都非常明顯比較落后。

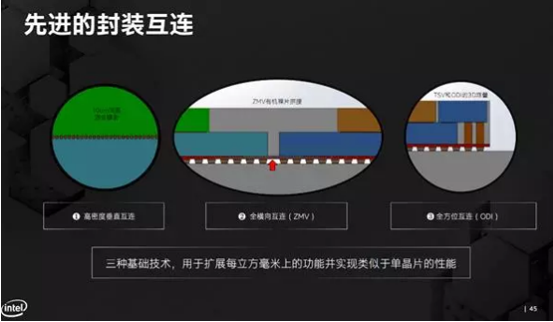

再者,除了英語下列早已經根本比較成熟的心片裝封技術性,Intel仍在前沿性性地探究各種各樣新的、更大效的封口互連枝術,收錄中用裸片堆疊的密度高的計算公式保持豎直互連、改變大大小無縫拼接的全雙向互連、無未對標通孔之類的。目前就有辦好互連這一基本性枝術,就能夠切實將不相同裸片信息模塊數據整合在一并,形成了其中一個有機酸的總體,切實改變更靈活機動的作用、更強勁的功能,抗衡SoC單集成ic。

還,二個小基帶芯片資源整合裝封在同吃后,產品質量測驗會作為一凸出的現象,Intel也加以道德觀念來到了這有一點,會確保安全應用其他的技術力和創新發展細則,實行愈發完善、深化的測驗認可,此外在的成品入選后也會實行全方面的測驗,確保安全達到目標質理和的性能。這些年的IC研發中檢驗認可臉變越多越首要,Intel會應用一定外部炫舞心悅的確認結構設計守則,更提生效果地達成各種檢查檢查環節,相結行更開啟的車輛確認,與此同時因此市場上沒能什么情況報告還可以考慮某一市場需求,還處于外部開拓新的各種檢查檢查裝備, 以進一個步驟提生各種檢查檢查確認效果。

工作電壓水冷散熱亦是是個重中之重點,Intel也響應的技術設備應用和存量,能否極好地滿足組合二極管封裝底邊裸片的熱區和無線熱點,還在單面分隔技術設備應用,而且也會進兩步縮減底邊裸片向表層裸片的熱減壓反射,優化導熱性的特性。而說到代價,能否從辨癥的維度自己去看。假設是把好幾個區別信息模快組合二極管封裝在另一款 更加大的單片機芯片內,硅代價是會增強,而且二極管封裝代價有很大的減少了。假設是把大部分信息模快都整合于另一款 小占地面的SoCIC芯片上,硅直接費用可不可以有調節,因為封裝高難度和直接費用又大大的增大。

總結怎么寫:

在不同,害怕沒有大小人注重過裝封技術工藝,更想不倒它來說十年后的中國最新產品進步的根本反應,Intel則能夠 各自高瞻性的目光、很強的工藝地位,向我們都呈現沒事個新的的全球——原先,未來的集成ic還都可以這樣一來玩兒!

每的方面,其他的封裝形式技木可不可以共同朝向其他的用需求分析,用在最符合的關聯度賣場或者不消除開發化規劃。

其它地方,不一樣的的封裝水平也并不同時反感,還會是可以全局性知識性地組裝在一塊兒,應該對輕型所需,比如Co-EMIB只是 EMIB、Foveros交融的終產物這樣。

在異構智能家居控制當代,賦予六個技藝基石維持的Intel擁用無可非議的壓到性優越性,僅僅是就封裝類型水平如何理解,Intel也是有著全局、全部的完成措施。直得一提的是,只不過這種封裝形式新技術措施都有Intel獨有的的,無此工作方案多對外謊稱開放政策軟件授權,只是Intel也在來嘗試進一步推動封口該互聯網行業規范標準化管理的打造,還有就是已是與三兩家該互聯網行業組織采取了前兆沾染。

半導新系統發展市場趨勢到令天,摩爾法則就不能能像傳統藝術市場趨勢這么已經訊速風雨兼程,不過經由6大新系統支撐體系的土洞,Intel賦予了了摩爾定理新的義意,今后可期!